Proceedings

# Workshop on Interaction between Compilers and Computer Architectures

February 3, 2002 Cambridge, MA

In conjunction with

**Eighth International Symposium on**

**High-performance Computer Architecture (HPCA-8)**

## The Sixth Annual Workshop on Interaction between Compilers and Computer Architectures (INTERACT-6)

February 3, 2001

Cambridge, MA

In conjunction with 8th International Symposium on High-performance Computer Architecture (HPCA-8)

Sponsored by IEEE Computer Society Technical Committee on Computer Architecture

### **Program Committee**

Chair: Gyungho Lee, Iowa State Univ. David August, Princeton Univ. Todd Austin, Univ. of Michigan Doug Burger, Univ. of Texas-Austin Kemal Ebcioglu, IBM Antonio Gonzalez, Universitat Politecnica de Catalunya, Spain Lizy John, Univ. of Texas-Austin Zhiyuan Li, Purdue Univ. Eric Rotenberg, North Carolina State Univ. Andre Seznec, IRISA, France INTERACT-6: The Sixth Annual Workshop on Interaction between Compilers and Computers Architectures

## **Advance Program**

I. Instruction Scheduling (9:00 am ~ 10:00pm)

Chair: G. Lee

Compiling for Fine-Grain Concurrency: Planning and Performing Software Thread Integration Alexander G. Dean Department of ECE, North Carolina State University

Dynamically Scheduling VLIW Instructions with Dependency Information Sunghyun Jee, Chonan College in Foreign Studies Kannappan Palaniappan, Department of CSCE, University of Missouri – Columbia

- Coffee Break (10:00 ~ 10:30am)

### II. Simulation and Profiling (10:30 ~ 12:00am)

Chair: A. Dean

Accuracy of Profile Maintenance in Optimizing Compilers Youfeng Wu Microprocessor Research Labs, Intel

Mastering Startup Costs in Assembler-Based Compiled Instruction-Set Simulation Ronan Amicel, and Francois Bodin IRISA / INRIA, France

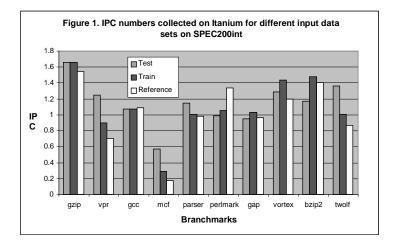

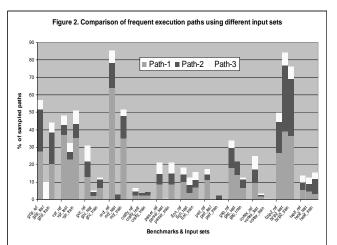

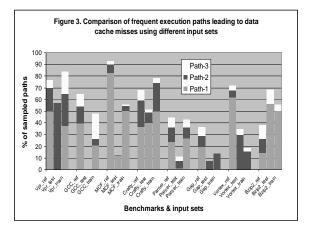

On the Predictability of Program Behavior Using Different Input Data Sets

Wei Chung Hsu, Howard Chen, Pen Chung Yew Department of Computer Science, University of Minnesota Dong-Yuan Chen, Microprocessor Research Labs, Intel

- Lunch Break (12:00 ~ 2:00pm)

### III. Data Access (2:00 ~ 3:00pm)

Chair: G. Lee

#### Quantitative Evaluation of the Register Stack Engine and Optimizations for Future Itanium Processors

R. Dave Weldon, Steven S. Chang, Hong Wang, Gerolf Hoflehner, Perry Wang, Dan Lavery and John Shen Microarchitecture Research Labs, Intel

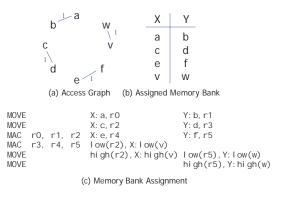

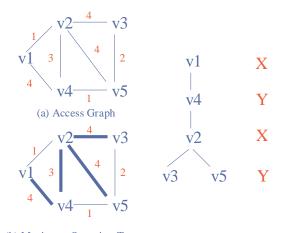

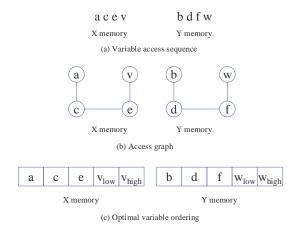

#### Efficient and Fast Data Allocation of On-chip Dual Memory Banks

Jeonghun Cho, Jinhwan Kim, and Yunheung Paek Department of EECS, Korea Advanced Institute of Science & Technology

- Coffee Break (3:00 ~ 3:30pm)

### IV. Code Size (3:30 ~ 5:00pm)

#### Chair: W. Hsu

Code Size Efficiency in Global Scheduling for ILP Processors Huiyang Zhou, and Thomas M. Conte Department of ECE, North Carolina State University

#### **Code Compression by Register Operand Dependency**

Kelvin Lin, Jean Jyh-Jiun Shann, and Chung-Ping Chung Department of CSIE, National Chiao Tung University

Code Cache Management Schemes for Dynamic Optimizers Kim Hazelwood, and Michael D. Smith

Division of Engineering and Applied Sciences, Harvard University

### **Compiling for Fine-Grain Concurrency: Planning and Performing Software Thread Integration**

Alexander G. Dean

Center for Embedded Systems Research, Department of Electrical and Computer Engineering NC State University, Raleigh, NC 27695

alex\_dean@ncsu.edu

#### Abstract

Embedded systems require control of many concurrent real-time activities, leading to system designs which feature multiple hardware peripherals with each providing a specific, dedicated service. These peripherals increase system size, cost, weight, power and design time. Software thread integration (STI) provides low-cost thread concurrency on general-purpose processors by automatically interleaving multiple (potentially real-time) threads of control into one. This simplifies hardware to software migration (which eliminates dedicated hardware) and can help embedded system designers meet design constraints such as size, weight, power and cost.

This paper introduces automated methods for planning and performing the code transformations needed for integration of functions with more sophisticated control flows than in previous work. We demonstrate the methods by using **Thrint**, our post-pass thread-integrating compiler, to automatically integrate multiple threads for a sample real-time embedded system with fine-grain concurrency. Previous work in thread integration required users to manually integrate loops; this is now performed automatically. The sample application generates an NTSC monochrome video signal (sending out a stream of pixels to a video DAC) with STI to replace a video refresh controller IC. Using Thrint reduces integration time from days to minutes and reclaims up to 99% of the system's finegrain idle time.

#### 1. Introduction

Embedded systems have multiple concurrent activities which must meet their deadlines or else the system will fail. These activities are usually implemented in hardware to guarantee they occur on time, as most microprocessors suffer when trying to perform multiple threads concurrently at a fine grain while meeting deadlines. Adding this hardware complicates system design whether added as external ICs or as modules on a microcontroller or system-on-chip. External components increase system size, weight, power, parts cost and design time. Integrated hardware peripherals increase design time and also fracture the chipmaker's market (which leads to increased cost through reduced volumes). In the end, both internal and external hardware solutions increase costs.

#### 1.1 Hardware to Software Migration Challenges

These costs have led to many efforts to implement the concurrent activities in software in order to ride the wave of falling compute costs described by Moore's law. There are two difficulties with making generic microprocessors adept at executing multiple concurrent threads.

First, the processor must switch easily among contexts, saving and restoring registers with each switch. There are many techniques (register banks and windows, coarse- and fine-grained multithreading, simultaneous multithreading, multiprocessing) to allow quick switches [22][33][31][32][7][30][6]. Some of these techniques are available in embedded processors, though not all.

Second, the processor must execute the right instructions from the right thread at the right time. This is the crux of the problem. The general solution is to divide threads into coarse- and fine-grain pieces. Each coarse piece is made of concatenated fine-grain pieces. Scheduling the fine-grain pieces is done statically (at compile time) and involves executing padding instructions to generate a given time delay. Nops are typically used. Although some coders have painstakingly managed to inject by hand instructions which perform useful work for another part of the program, the resulting programs are brittle and difficult to maintain. Furthermore, this approach is very poorly suited to systems which require frequent real-time activity with fine timing accuracy.

Despite these difficulties, there is an abundance of articles and application notes from makers of microcontrollers describing how to extract concurrency from their generic processors [3] [4] [13] [14] [19] [20] [23] [24]. These efforts primarily target two classes of applications: video signal generators and communication protocol controllers. This paper is in the first area. The second area is much more demanding, and we are currently extending our STI concepts to support it.

#### 1.2 HSM with STI

We have developed and continue to enhance our compiler-based approach to providing fine-grain concurrency. We have developed a compiler *Thrint* which automatically creates an implicitly multithreaded function from two functions, one with real-time requirements on specific instructions. It implements many of the time-driven code transformations which we developed for integrating threads while maintaining control, data and timing correctness. With this technology an off-the-shelf uniprocessor can efficiently perform multiple concurrent functions without any special support for rapid context switching, scheduling or concurrency. This in turn makes hardware to software migration (HSM) viable.

Our past work developed concepts and methods not only for software thread integration (STI) but also how to use it for HSM, in which a real-time guest thread replaces the dedicated hardware and is integrated with one or more host threads from the application. We created a practical design procedure based upon idle time analysis of guest threads (to determine which threads have enough idle time to be worth integrating), temporal determinism of host threads (to determine which threads have enough timing determinism to be good frameworks for integration), methods for recognizing guest trigger events, methods for dispatching integrated threads, and techniques to predict overall performance of an integrated system. We derived methods for measuring the performance of the integrated software for peak and average cases as well [9][10][8][12].

In this paper we present the algorithms used to plan and then perform integration, using previously developed integration transformations as building blocks. We use two phases to enable the evaluation of a variety of integration plans using estimates of MIPS recovered, guest response latency and code expansion. This enables the compiler or the designer to select the best approach for integration. An NTSC video refresh application is used to demonstrate the automated use of the integration planning and execution methods presented here. We use our compiler *Thrint* for the integration; it now totals over 10,000 lines of C++ code in 20 modules. We examine an application and use *Thrint* to perform the video refresh work, creating efficient integrated functions.

This paper has the following organization. Section 2 gives an overview of how STI works. Section 3 introduces the planning and transformation algorithms and data structures used in *Thrint*. Section 4 examines the integration of a sample application. Section 5 summarizes the results and their broader implications.

#### 2. Software Thread Integration Overview

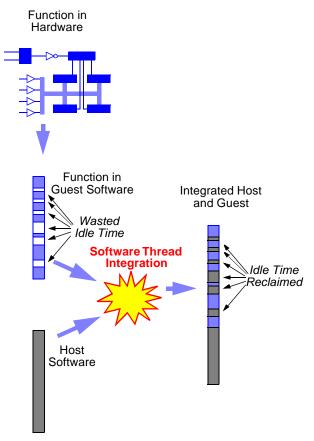

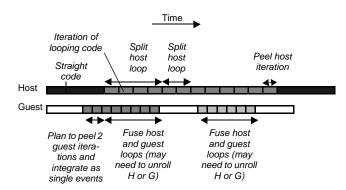

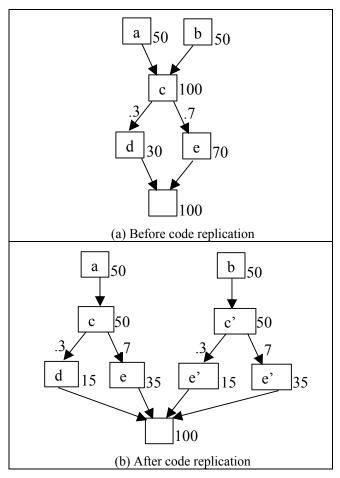

Figure 1 presents an overview of how STI is used for HSM. A hardware function is replaced with software written by a programmer. This code consists of one or more guest threads (represented by the blue bar) with real-time requirements. When the threads are scheduled for execution on a sufficiently fast CPU, gaps will appear in the schedule of guest instructions, as illustrated by the white gaps in the blue bar. These gaps are pieces of idle time which can be reclaimed to perform useful host work. STI recovers fine-grain idle time efficiently and automatically.

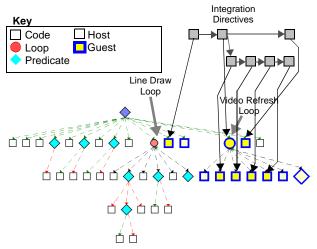

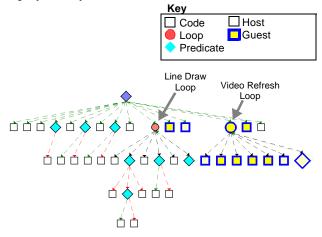

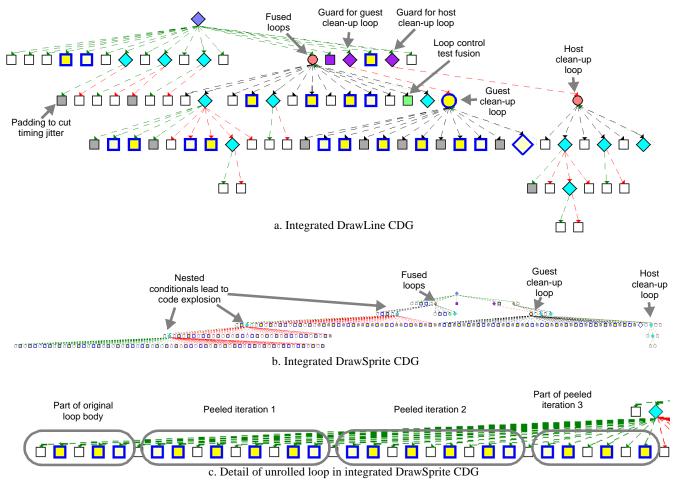

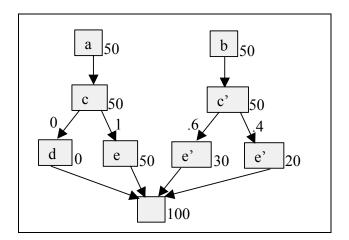

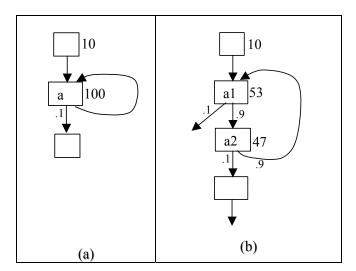

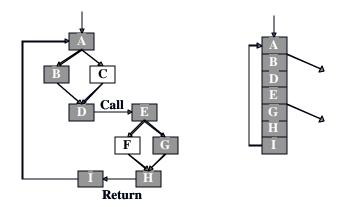

STI uses a control dependence graph (CDG, a subset of program dependence the graph [1][15][17][18][26][27][29]]) to represent each procedure in a program. In this hierarchical graph (please see Figure 2), control dependences such as conditionals and loops are represented as non-leaf nodes, and assembly instructions are stored in leaf nodes. Conditional nesting is represented vertically while execution order is horizontal, so that an in-order left-to-right traversal matches the program's execution. The CDG is a good form for holding a program for STI because this structure simplifies analysis and transformation through its hierarchy. Program constructs such as loops and conditionals as well as single basic blocks are moved efficiently in a coarse-grain fashion, yet the transformations also provide fine-grain scheduling of instructions as needed.

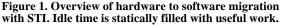

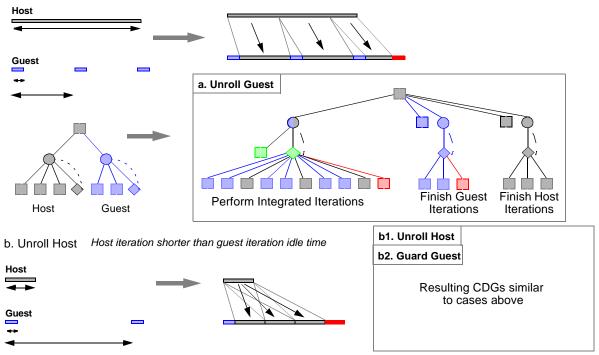

Using STI for HSM involves moving guest code into the correct position within the host code for execution at the correct time. The first stage in this code motion is called degenerate integration; the programmer manually appends the guest procedure code to the end of the host procedures. The resulting procedure is then automatically integrated by moving guest nodes left in the CDG to locations which correspond to the target time ranges. A tight target time range may fall completely within a host node, forcing movement down into that node or its subgraph. As shown in Figure 2, we have developed a set of CDG transformations [10][11][12] which can be applied repeatedly and hierarchically, enabling code motion into a variety of nested control structures. For example, moving a single guest event node into a host code node requires splitting the code node (a basic block). This is shown in the diagram as single event case b. Moving into a conditional (a predicate) requires guest replication into each case (single event case c). Moving into a loop requires loop splitting (single event case d1) or guarded execution (single event case d2) on a specific iteration. The transformations also support the integration of guest loops with host loops. Loop fusion, guarding and unrolling are used to match the host loop's work with the available idle time within one or more guest iterations. Most of these transformations are implemented in our thread integrating compiler *Thrint*.

STI automatically ensures semantic and timing correctness with its transformations. The variety of integration methods and decisions enable the STI tool to automatically optimize for execution speed or code size.

All control and data dependences must be observed to ensure semantic correctness. The CDG explicitly represents control dependences as graph structures; STI's code transformations modify the graph yet maintain these dependences. These transformations enable STI to interleave code from different threads, which is the key to reclaiming idle time efficiently. STI only needs to handle false data dependences when integrating threads; no other data dependency issues arise because each individual thread remains in order. Assembly code contains many false data dependences because of register reuse, so STI automatically reallocates registers to remove this constraint and make code motion easier.

All real-time dependences must be observed to ensure timing correctness. Each RT guest instruction must be moved to execute within its target time range. STI automates this process. First the host and guest threads are statically analyzed for timing behavior [25][28], with best and worst cases predicted. Hardware and software both conspire to make this a difficult problem in the general case. However, we focus on applications without recursion or dynamic function calls, and processors without superscalar execution, virtual memory or variable latency instructions. We assume locked caches or fast on-chip memory and no pipelining.

For perspective, in 1999 81% of the 5.3 billion microprocessors sold were four- and eight-bit units (9% were 16-bit). These MCUs run applications which are not computationally intensive, and do not need more parallelism or faster clock rates. Instead they are constrained by other issues such as functionality, cost, power dissipation, design time and use of commercial off-the-shelf products.

#### Looping Event Integration

a. Unroll Guest Host iteration longer than guest iteration idle time

Figure 2. Summary of Single and Looping Event Code Transformations for STI

The fact that microarchitectural features such as superscalar execution and memory caches complicate the static timing analysis upon which STI relies is irrelevant for these applications, as they do not need the performance proided by these features. In fact, often these applications cannot afford the additional cost of such an enhanced processor.

During integration, timing directives (supplied by the programmer) guide integration. Timing jitter in the host thread is automatically reduced (using padding instructions) to meet guest requirements. The CDG's structure makes the timing analysis and integration straightforward.

STI produces code which is more efficient than context-switching or busy-waiting. The processor spends fewer cycles performing overhead work. The price is expanded code memory. STI may duplicate code, unroll and split loops and add guard instructions. It may also duplicate both host and guest threads. Memory may be cheap, but it is not free. The memory expansion can be reduced by trading off execution speed or timing accuracy. This flexibility allows the tailoring of STI transformations to a particular embedded system's constraints.

#### 3. Planning and Performing Integration

Integration requires several stages of preparation. Time-critical guest code is identified based upon user directives, the host code's execution schedule is predicted for both best and worst cases, and temporally deterministic segments within the host are identified as targets for integration (as described in [11]). Next, integration planning takes place. Thrint plans the integration transformations needed to integrate the guest function with each of the temporally deterministic segments identified previously. The guest code is then integrated with one or more of these temporally deterministic segments.

The guest thread consists of nodes (code, loop, predicate), some of which may have timing requirements associated with them (code and loop). These are sub-thread timing requirements; thread-level timing requirements are dealt with elsewhere. We use timing directives to specify the target time (with a user-defined tolerance) for the start of the node's execution, as represented as a delay from the beginning of the integrated thread's execution. We call guest nodes with these timing requirements *explicitly specified guests* (or simply *explicit guests*); the other guest nodes are

called *implicit guests*. Thread integration must place the explict guests in the host code based on the timing directives, while the implicit guests are merely constrained to be moved to ensure in-order execution between the explicit guests.

```

PROCEDURE DrawSprite INTO DrawSprite

TOLERANCE 0

BLOCK Video_Reset_Ptr AT 10

LOOP Video_Loop PERIOD 40 ITERATION_COUNT 128

BLOCK Video_Pix0 INTO_LOOP Video_Loop FIRST_AT 22

BLOCK Video_Pix1 INTO_LOOP Video_Loop FIRST_AT 32

BLOCK Video_Pix2 INTO_LOOP Video_Loop FIRST_AT 42

BLOCK Video_Pix3 INTO_LOOP Video_Loop FIRST_AT 52

BLOCK Video_End IMPLICIT

END

```

### Figure 3. DrawSprite integration directives file specifies timing requirements for guest thread components

The integration requirements are defined in a text file as shown in Figure 3. They are loaded into a data structure which duplicates the CDG structure of the explicit guest nodes, as shown in Figure 4.

Figure 4. Initial DrawLine control dependence graph with integration directives data structure marking explicit guests

Each integration directive node holds a pointer to its explicit guest node, as well as a list of pointers to the implicit guests which precede and follow the explicit guest. Currently we limit explicit guests to be code or loop nodes which are at the first or second level of the CDG. We have found this to be adequate for a variety of applications. An implicit guest may be arbitrary code, provided that it is structured.

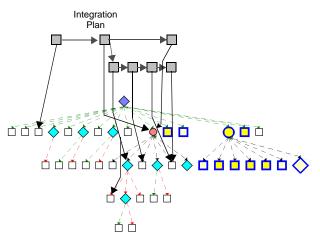

At this point integration planning begins, using the temporally deterministic segments [11] identified elsewhere (each of these is a contiguous subgraph of the host CDG). The algorithm Plan\_Integration (Figure 5) is used to identify which transformations are needed to integrate the guest code with the host segment. Plan\_Integration creates an integration plan based on the integration directives data structure created previously, and then steps through each explicit guest within it.

| IntegrationDirectives::Plan_Integration(host_segment) {   |

|-----------------------------------------------------------|

| for each explicit guest in integration directives list    |

| if current guest is single guest event                    |

| host_segment->get_first_node->find_host for current guest |

| else // is looping guest event                            |

| while guest loop iterations remain                        |

| find time covered by these guest iterations               |

| if host loop execution overlap                            |

| for each host loop executing during this time (in order)  |

| if guest loop starts first                                |

| peel preceding iterations from guest loop                 |

| plan integration as multiple non-looping guests           |

| else if host loop starts first                            |

| split preceding host loop iterations                      |

| if overlap time of host and guest loops is enough         |

| plan to unroll guest or host loop                         |

| mark for fusion                                           |

| if loop iterations remain                                 |

| mark for clean-up loop copies                             |

| else no host loops during guest loop                      |

| peel all loop iterations                                  |

| plan their integration as multiple non-looping guests     |

| }                                                         |

#### Figure 5. Plan Integration finds hosts, planning loop transformations as needed to fuse loops

Integration for code guest nodes is handled by calling Find\_Hosts (Figure 6). This algorithm identifies which node(s) will be executing during the guest's target time range, and determines which transformations (previously presented in Figure 2) are needed to ensure that if the guest is placed there, control-flow and timing requirements are met. This may involve determining where to split a loop or how many padding nops to use for balancing a predicate node.Figure 7 shows which target host nodes are identified for the example presented later in this paper.

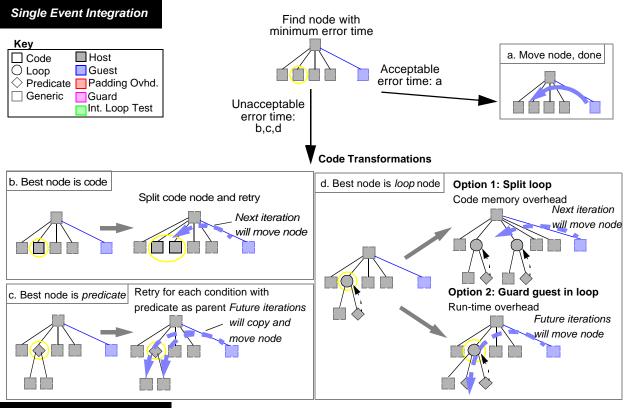

Looping guest events require a more sophisticated approach, which is listed in Figure 5 (an example is graphically presented in Figure 8). The technique attempts to perform loop fusion if a guest and host loop overlap for multiple iterations. The goal of this loop fusion (as seen in Figure 2) is to match guest loop idle time with host loop body work through unrolling.

Guarded clean-up loops can be added following the fused loop body accomodate extra iterations or unknown loop counts. The portions of loops which do not overlap are handled differently depending upon type. Host loops are split to separate the overlapping and non-overlapping iterations. Guest loops have iterations peeled off, with each explicit guest in the unrolled iteration integrated as a non-looping guest node.

#### Node::Find\_Hosts(target\_time, guest\_node\_integration\_plan) { if this node finishes executing before target\_time call Find\_Hosts(target\_time) on later sibling else plan to pad node if needed to remove unacceptable jitter if target time follows padded node // can execute guest immediately after this node guest\_node\_integration\_plan->Add\_Host(this, AFTER) else // descend into this node for better timing accuracy switch on this node's type CODE: guest\_node\_integration\_plan->Add\_Host(this, WITHIN) PREDICATE. // descend into condition subgraphs for each condition this->Get\_First\_Child(condition)->Find\_Hosts(target\_time, quest node integration plan) LOOP: // descend into loop subgraph if quest node is not in loop // plan to split host loop or guard guest within it this->Find\_Hosts\_In\_Loop(target\_time, quest node integration plan) else // Plan\_Loop\_Integration() has already planned loop // fusion, so just locate guests in appropriate hosts // without additional loop transformations this->Get\_First\_Child()->Find\_Hosts(target\_time, quest node integration plan)

## Figure 6. Find\_Hosts algorithm identifies host nodes and transformations to ensure guest begins execution within target\_time range

}

Figure 7. Integration plan data structure identifies locations in host code corresponding to guest target times

### Figure 8. Diagram showing example of loop integration planning with fusion, splitting and peeling

This completes the planning for integration, allowing the evaluation of interesting evaluation plans to trade off code memory expansion for increased performance. One or more such integration plans may be selected for actual integration, as described in [12].

| DeterministicCodeSegment::Integrate(integration_plan) {           |

|-------------------------------------------------------------------|

| for each top_level_guest                                          |

| if guest is loop                                                  |

| for each host of top-level guest                                  |

| if current host is loop transform                                 |

| do loop transformation to prepare for fusion                      |

| make guarded copy of guest loop after host loop if needed         |

| cur_guest = top_level_guest's first child                         |

| else                                                              |

| cur_guest = top_level_guest                                       |

| do                                                                |

| pad previous nodes if needed to cut start time jitter             |

| pad host node if needed to cut host node's completion time jitter |

| for each of cur_guest's hosts cur_host                            |

| do any host loop transformations (e.g. splitting)                 |

| update cur_host pointer based on previous guests, host            |

| splitting and padding                                             |

| insert these guest node clones at cur_host:                       |

| cur_guest's previous implicit guest nodes                         |

| cur_guest (explicit guest) node                                   |

| cur_guest's following implicit guest nodes                        |

| advance cur_host                                                  |

| if cur_guest within guest loop                                    |

| advance to next guest within guest loop                           |

| else                                                              |

| cur_guest = NULL                                                  |

| while cur_guest                                                   |

| for each top_level_guest                                          |

| create and insert fused loop control tests                        |

### Figure 9. Integrate algorithm implements code transformations planned previously

}

Integration, presented in Figure 9, performs padding, loop splitting, unrolling and other transformations previously planned and then copies the guest nodes to the appropriate locations in the host code. Note that each explicit guest may be assigned multiple hosts, and each explicit guest may have multiple implicit guests.

#### 4. STI for Video Application

Our previous work has developed concepts, code transformations and analytical methods for performing STI especially for HSM. Previous thread integration results reflect manually integrated code and a mix of manual and automatic analysis. In this paper we demonstrate automatic thread integration using our post-pass compiler *Thrint*, which implements automatic thread analysis, visualization, and integration by using techniques of control- and data-flow analysis, static timing analysis, code transformations and register real-location. We first examine the application, then evaluate idle time within the guest thread and temporal determinacy within the host threads. We then analyze automatically integrated code for system efficiency and memory expansion.

## **4.1** Target System for Hardware to Software Migration

To demonstrate the benefits of STI for HSM we use an NTSC video refresh controller application (for driving a CRT). We replace a video generator chip with a software version. The processor must generate an NTSC-compatible monochrome video signal [16], summarized in Figure 10. Although the beam scans 525 times per frame (in two interlaced passes (fields) per 33.3 ms frame), only 494 rows are visible and require video data, corresponding to 75.8% of the processor's time. There are additional features in a video signal (vertical sync, serration and equalization pulses) but these can be generated easily with standard methods (ISRs triggered by an on-chip timer) so we do not examine them in this work. The video data portion of the signal is the most demanding, as a pixel of video data must be generated every 100 ns (for 512 pixels per row). With a 100 MHz CPU this corresponds to ten clock cycles per pixel, which is very frequent and offers little time for context switching or scheduling.

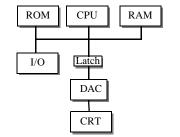

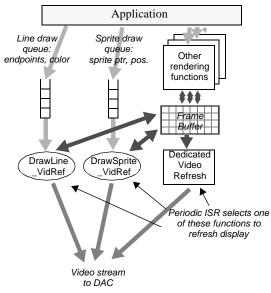

We target a 32 bit scalar RISC processor running at 100 MHz with on-chip single-cycle memory access and instruction execution and no virtual memory. The processor executes 100 million instructions per second. The hardware is structured as shown in Figure 11.

Figure 11. Hardware architecture of system lacks a video refresh controller

The system is designed to generate a monochrome 512x494 pixel image with eight bits per pixel. A digital-to-analog converter (DAC) converts the data byte to an analog voltage for the CRT. Note that this design

Figure 12. Video data flow overview

can easily be extended to provide color video to a CRT with RGB inputs by adding two more DACs and a look-up table (palette) memory.

We assume a periodic interrupt will trigger an ISR just before the beginning of the video data portion of each row, and that this ISR examines two queues which hold data to be used by two functions which have been integrated with display refresh code. The queues hold parameters for drawing lines or sprites and are fed by other functions in the application. The ISR selects one of the two integrated functions (if data is present in the queue) or else a dedicated busy-wait refresh function. The chosen thread then reads video data from the frame buffer in memory and sends it out to the CRT through the DACs. The ISR and the queues are not implemented for this paper because they are straightforward to implement and analyze. Instead we focus on the integration and analysis of the refresh/render threads which are integrated by the compiler.

#### 4.2 Experimental Method

Our compiler *Thrint* processes functions compiled for the Alpha instruction set architecture. Although it is not representative of most embedded systems, it was chosen to leverage the compiler *PCOM* from another tool suite (*Pedigree* [26]). The Alpha ISA is a clean load-store architecture with an ample register set and is a suitable target for this work. We assume a microarchitecture with easily predicted performance: scalar execution, single-cycle memory system or lockable cache, a predictable pipeline and no virtual memory. As explained in the introduction, the bulk of the applications targeted by this research neither need nor can afford the high throughputs provided by sophisticated and complex microarchitectures.

The guest (VidRef) and host functions (DrawLine [2] and DrawSprite) are written in C++ and used for initial degenerate integration (the guest function body is concatenated with the host function body, and automatic variables are copied). The new functions are compiled with gcc 2.7 with -O1 optimization. Basic block labels are added to the resulting assembly language functions to identify instructions with specific real-time requirements. The functions are then processed by PCOM into CDG-structured assembly language. These functions are analyzed and integrated by Thrint, which creates an output assembler file as well as visualization support files (e.g. Figure 14). Data symbol information is added to the assembler file (after having been deleted during processing) and then assembled. The object file is linked with an X-windows-based driver program to allow execution-based verification of program operation. Timing correctness is verified by static timing analysis in Thrint after all code transformations have been completed. As the target machine architecture is highly predictable (compredictable pipeline, scalar instruction pletely execution, single-cycle memory access), timing verification through execution or simulation is not performed.

#### 4.3 Guest Thread

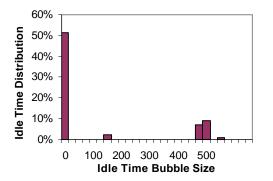

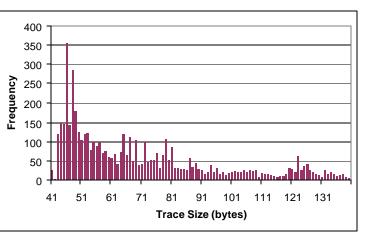

The video signal has events which must occur within tight time ranges to create a compatible video signal. As mentioned previously, we assume an interrupt service routine triggered by a programmable timer generates the signal transitions needed for the horizontal and vertical sync, front and back porches, and equalization and serration pulses. The video data is read out of a frame buffer and sent out through an 8 bit DAC by the previously mentioned VidRef function. When the software needed to perform these events is executed by the 100 MHz processor (without any context switching or scheduling overhead considered), the resulting idle time is distributed as shown in Figure 13.

Figure 13. Idle time in video signal generation software is mostly fine-grain

The idle time in large bubbles (compared with the overhead of setting up a timer and performing two context switches (e.g. 30 cycles) is best recovered through context switching. The idle time in smaller bubbles is recovered through STI. Figure 13 shows that over half the processor's idle time for this video refresh application is in fine-grain pieces of idle time (four, seven and eight cycles), making this type of application a good fit for HSM using STI.

#### 4.4 Host Threads

Figure 14 shows the control structure of DrawLine after the guest code has been appended and the file assembled. DrawLine takes two endpoints and a color code as arguments and scan converts the line into the frame buffer. Two conditionals (predicates) in the beginning of the function determine line direction, then the code determines increment values and finally a loop sets pixels in the frame buffer. The conditionals within the loop selectively update x or y counters and error variables. The guest code consists of pointer initialization code and then a loop which loads 32-bit words from memory and sends them out to the video display one byte at a time.

Figure 14. Initial DrawLine Control Dependence Graph

Figure 15 shows the control structure for Draw-Sprite with the guest code appended. DrawSprite takes a pointer to a sprite (a 16x16 pixel array) with a position and draws the sprite in the frame buffer. The code consists of a loop which iterates across sprite rows, and conditionals within that body which handle various position cases of the sprite. The guest code is the same as for DrawLine.

Figure 15. Initial DrawSprite Control Dependence Graph

#### 4.5 Integration Process

The code is prepared for integration by marking time-sensitive instructions in the guest thread assembly code (called *explicit guests*) with labels, and then specifying timing requirements for those basic blocks. Figure 3 presents the integration directives file used for integrating DrawSprite. A timing error tolerance of 0 cycles is specified, so *Thrint* pads away all timing jitter (leading to increased code size). Only explicit guests (nodes with specific timing requirements) need to be defined in this file; the intervening nodes are called *implicit guests* and are automatically handled. At this point *Thrint* is run to perform integration.

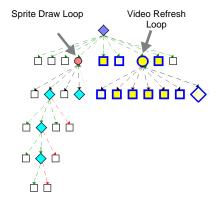

Figure 16 shows the CDGs of the two integrated functions. Figure 16.a shows that DrawLine's host loop is fused with the video refresh loop, and guest code is replicated into one host conditional. The loop control tests are fused with a logical AND to control loop execution. After the fused loop finishes, a guarded dedicated guest loop completes any remaining video refresh work. It is guarded to keep it from running if there is no more work. Following that loop is a guarded replica of the host loop to finish drawing long lines which were not completed in the fused loop. Figure 16.b shows DrawSprite integrated with VideoRefresh. The idle time in each iteration of the guest loop (27 cycles) is not long enough to hold a full host loop iteration (up to 107 cycles). *Thrint* unrolls the guest loop by ceil(107/27) = 4 times to fit the host within the idle time. Figure 16.c shows that part of the integrated unrolled loop has been copied into the taken case of a host predicate (conditional). The three nested levels of conditionals within DrawSprite lead to significant expansion because most of the guest code is replicated into these cases. Apart from this difference, the resulting code is similar in structure to the other example, with a dedicated guest clean-up loop followed by a host clean-up loop.

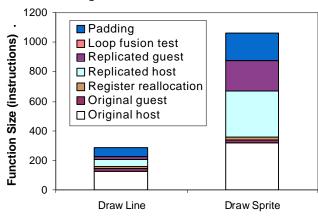

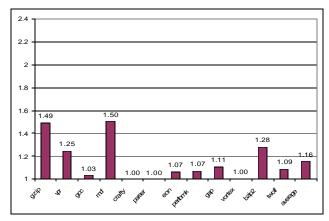

#### 4.6 Code Expansion

Figure 17. Code expansion for integrated threads

Figure 17 shows how STI affects function size for the examples used. DrawLine grows by 96% (from 144 to 282 instructions) and DrawSprite grows by 211% (from 341 to 1062 instructions). The bulk of the code expansion for DrawLine() (57 instructions) comes from padding to equalize timing variations among paths and to statically schedule the dedicated guest clean-up loop. Next are 47 instructions from splitting the host loop (marked "Replicated Host" in the graph). The guest requires some replication into conditionals, adding 18 instructions.

DrawSprite() grows first because its 312-instruction host loop is split to allow integration with its first 11 iterations. Next, the guest replication adds 206 instructions because the guest loop is unrolled three times, and much of that code must be replicated into each path of the three-conditional deep host loop. In addition, 187 padding instructions are added to statically schedule the guest code and reduce timing variations in the host code. Clearly the combination of deep conditionals and loop unrolling leads to code explosion; it would be logical to examine the DrawSprite function and replace the conditionals (which allow sprites to be drawn at positions unaligned with word boundaries) with computation.

This code expansion only applies to functions which are integrated. In a typical application there would only be a few, so the overall impact on code size would be slight.

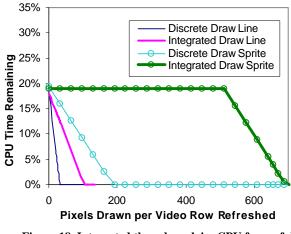

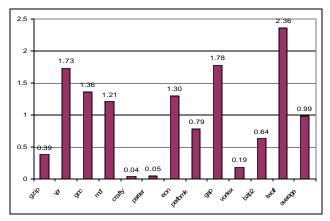

#### 4.7 Performance

Using STI to reclaim the idle time within the video refresh portion enables the system to perform more

useful work such as line or sprite drawing. Figure 18 shows the system behavior as a function of line or sprite drawing performed per video row. The vertical axis presents the fraction of CPU time remaining after performing both video refresh and either line or sprite drawing. We examine the cases of a discrete video refresh (with all idle time filled with nops) and the integrated versions described previously. Performing the video refresh without line or sprite drawing immediately reduces free time to 18% for both implementations. However, as graphics work is added, the integrated version is able to recover idle time to perform useful work, raising drawing throughput for lines by 225% and sprites by 290% (X-axis intercepts).

Figure 18. Integrated threads reclaim CPU for useful work, improving performance

The initially horizontal slope of the integrated DrawSprite shows that it recovers all available idle time. The non-horizontal slope of DrawLine shows that the overhead of integration consumes a significant amount of idle time.

#### 5. Conclusions and Current Work

We have developed an automated solution to the hardware-to-software migration challenge called software thread integration. Our compiler *Thrint* automatically integrates multiple threads into a single implicitly multithreaded flow of control which executes on a standard uniprocessors without special support for scheduling or fast context switching. We have also developed design methods for using software thread integration to perform hardware to software migration quickly and efficiently.

In this paper we present the data structures and algorithms needed to plan and perform software thread

integration, using the transformations developed in previous work. These methods have been implemented in our research compiler Thrint. We demonstrate the results of automatic integration of a sample application with fine-grain concurrency and analyze the resulting code expansion.

We use *Thrint* and STI to replace a video refresh controller with a software implementation. We reduce integration time from days to minutes, paying a minor penalty in memory size while reclaiming large amounts of idle time.

#### 6. References

[1] V.H. Allan, J. Janardhan, R.M. Lee and M. Srinivas:

Enhanced Region Scheduling on a Program Dependence Graph, *Proceedings of the 25th International Symposium and Workshop on Microarchitecture (MICRO-25)*, Portland, OR, Dec. 1-4, 1992 [2] J.E. Bresenham, "Algorithm for Computer Control of a Digi-

tal Plotter." IBM Systems Journal, 4(1), 1965, pp. 25-30

[3] Tony Breslin, "68HC05K0 Infra-Red Remote Control,"

Motorola Semiconductor Application Note AN463, 1997 [4] Dave Bursky, "Speedy 8-Bit Microcontroller Crafts Virtual Peripherals," *Electronic Design*, August 4, 1997

[5] G.J. Chaitin, "Register Allocation & Spilling via Graph Coloring," *Proceedings of the SIGPLAN '82 Symposium on Compiler Construction*, pp. 98-105, June 1982

[6] D. Culler, "Fine-Grain Parallelism with Minimal Hardware Support: A Compiler-Controlled Threaded Abstract Machine," Proc. 4th Intl. Conf. on Architectural Support for Programming Languages and Operating Systems, April 1991

[7] Y. Chou, D. Siewiorek, J. Shen. "A Realistic Study on Multithreaded Superscalar Processor Design" Europar '97, Passau, Germany, August 1997

[8] Alexander G. Dean and Richard R. Grzybowski, "A High-Temperature Embedded Network Interface using Software Thread Integration," Second Workshop on Compiler and Architectural Support for Embedded Systems, Washington, DC, October 1-3 1999

[9] Alexander G. Dean and John Paul Shen, "Hardware to Software Migration with Real-Time Thread Integration," Proceedings of the 24th EUROMICRO Conference, Västerås, Sweden, August 25-27 1998, pp. 243-252.

[10] Alexander G. Dean and John Paul Shen, "Techniques for Software Thread Integration in Real-Time Embedded Systems," Proceedings of the 19th Symposium on Real-Time Systems, Madrid, Spain December 2-4 1998, pp. 322-333

[11] Alexander G. Dean and John Paul Shen, "System-Level Issues for Software Thread Integration: Guest Triggering and Host Selection," Proceedings of the 20th Symposium on Real-Time Systems, Scottsdale, Arizona, December 1-3 1999, pp. 234-245

[12] Alexander G. Dean, "Software Thread Integration for Hardware to Software Migration," Doctoral Thesis, Carnegie Mellon University, Pittsburgh, PA, May 2000

[13] Martin Embacher, "Replacing Dedicated Protocol Controllers with Code Efficient and Configurable Microcontrollers -- Low Speed CAN Network Applications," National Semiconductor Application Note 1048, August 1996 [14] Scott Fink, "Hardware/Software Trade-offs in Microcontroller-based Systems," Application Note, Microchip Inc., 1997

[15] Jeanne Ferrante, Karl J. Ottenstein and Joe D. Warren: The Program Dependence Graph and Its Use in Optimization, *ACM Transactions on Programming Languages*, July 1987, 9(3):319-349

[16] B. Grob, **Basic Color Television Principles and Servicing**, McGraw Hill, 1975

[17] Rajiv Gupta and Mary Lou Soffa: Region Scheduling, *Proceedings of the Second International Conference on Supercomputing*, pp. 141-148, 1987

[18] Rajiv Gupta and Madalene Spezialetti: Busy-Idle Profiles and Compact Task Graphs: Compile-time Support for Interleaved and Overlapped Scheduling of Real-Time Tasks, *15th IEEE Real Time Systems Symposium*, pp. 86-96, 1994

[19] Scott George, "HC05 Software-Driven Asynchronous Serial Communication Techniques Using the MC68HC705J1A," Motorola Semiconductor Application Note AN1240

[20] Thomas F. Herbert, "Integrating a Soft Modem," *Embedded Systems Programming*, 12(3), March 1999, pp. 62-74

[21] HD61830/HD61830B LCDC (LCD Timing Controller) Data Sheet. Hitachi, Inc.

[22] Yasuo Hidaka, Hanpei Koike and Hidehiko Tanaka, "Multiple Threads in Cyclic Register Windows," Proceedings of the 20th International Symposium on Computer Architecture, San Diego, CA, May 1993

[23] Stephen Holland, "Low-Cost Software Bell-202 Modem," *Circuit Cellar*, June 1999, #107, pp. 12-19

[24] Robert Lacoste, "PIC' Spectrum Audio Spectrum Analyzer," *Circuit Cellar*, September 1998, #98, pp. 24-31

[25] Sharad Malik, Margaret Martonosi and Yau-Tsun Steven Li: Static Timing Analysis of Embedded Software, *ACM Design Automation Conference*, June 1997.

[26] Chris J. Newburn, Derek B. Noonburg and John P. Shen: A PDG-Based Tool and Its Use in Analyzing Program Control Dependences, *International Conference on Parallel Architectures and Compilation Techniques*, 1994

[27] Chris J. Newburn, Exploiting Multi-Grained Parallelism for Multiple-Instruction Stream Architectures, Ph.D. Thesis,

CMµART-97-04, Electrical and Computer Engineering Department, Carnegie Mellon University, November 1997

[28] P. Puschner and C. Koza: Calculating the maximum execution time of real-time programs. *The Journal of Real-Time Systems*, 1(2):160-176, September 1989

[29] Madalene Spezialetti and Rajiv Gupta: Timed Perturbation Analysis: An Approach for Non-Intrusive Monitoring of Real-Time Computations, *ACM SIGPLAN Workshop on Language, Compiler, and Tool Support for Real-Time Systems*, Orlando, Florida, June 1994

[30] R. Thekkath and S.J. Eggers, "The Effectiveness of Multiple Hardware Contexts," Proc. 6th Intl. Conf. on Architectural Support for Programming Languages and Operating Systems, 1994

[31] Toshiba America Electronic Components, Inc., "Clock Speeds Double With 20MHz Neuron Chips," Press Release, September 28 1997

[32] Toshiba America Electronic Components, Inc.,

"TMPN3120A20M, TMPN3120A20U Data Sheet," August 1998 [33] Carl A. Waldspurger and William E. Weihl, "Register Relocation: Flexible Contexts for Multithreading," Proceedings of the 20th Annual International Symposium on Computer Architecture, San Diego, CA, May 1993

### Dynamically Scheduling VLIW Instructions with Dependency Information

Sunghyun Jee Chonan College in Foreign Studies Chonan, Chungnam, South Korea jees@missouri.edu

#### Abstract

This paper proposes balancing scheduling effort more evenly between the compiler and the processor, by introducing dynamically scheduled Very Long Instruction Word (VLIW) instructions. Dynamically Instruction Scheduled VLIW (DISVLIW) processor is aimed specifically at dynamic scheduling VLIW instructions with dependency information. The DISVLIW processor dynamically schedules each instruction within long instructions using functional unit and dynamic scheduler pairs. Every dynamic scheduler dynamically checks for data dependencies and resource collisions while scheduling each instruction. This scheduling is especially effective in applications containing loops. We simulate the architecture and show that the DISVLIW processor performs significantly better than the VLIW processor for a wide range of cache sizes and across various numerical benchmark applications.

#### 1. Introduction

Recent high performance processors have depended on Instruction Level Parallelism (ILP) to achieve high execution speed. ILP processors achieve their high performance by causing multiple operations to execute in parallel using a combination of compiler and hardware techniques. Very Long Instruction Word (VLIW) is one particular style of processor design that tries to achieve high levels of ILP by executing long instructions composed of multiple instructions. The VLIW processor has performance bottlenecks due to static instruction scheduling and the unoptimized large object code containing a number of NOPs (No OPerations) and LNOPs (Long NOPs), where the LNOP means a long instruction that has only NOPs [20~22]. Superscalar VLIW (SVLIW) is the improving style of VLIW processor design that tries to execute object code constructed by removing all LNOPs from VLIW code [14,15,21,22]. The SVLIW processor also has a performance limitation similar to the VLIW processor due to static scheduling. By making use of powerful features to generate high-performance code, the IA-64 architecture Kannappan Palaniappan University of Missouri Missouri, Columbia, U.S.A. palani@cecs.missouri.edu

allows the compiler to exploit high ILP using Explicit Parallel Instruction Computing (EPIC) [23,24]. The IA-64 is a statically scheduled processor architecture where the compiler is responsible for efficiently exploiting the available ILP and keeps the executions busy [24]. Instead of the merits, the IA-64 processor has a performance limitation due to static instruction scheduling. In order to overcome current performance bottlenecks in modern architectures, a processor architecture that satisfies the following criteria is required: (1) balanced scheduling effort between compile-time and run-time, (2) dynamic instruction scheduling, and (3) reducing the size of object code.

This paper presents a new ILP processor architecture called Dynamically Instruction Scheduled VLIW (DISVLIW) that achieves these goals. The DISVLIW instruction format is augmented to allow dependent bit vectors to be placed in the same VLIW word. Dependent bit vectors are added to the instruction format to enable synchronization between prior and subsequent instructions. To schedule instructions dynamically, the DISVLIW processor uses functional unit and dynamic scheduler pairs. Every dynamic scheduler decides to issue the next instruction to the associated functional unit, or to stall the functional unit due to possible resource collisions or data dependencies among instructions per every cycle. Such features can reduce the total number of execution cycles of the DISVLIW processor better than those of the VLIW or the SVLIW processor that compulsorily schedules long instructions. The DISVLIW processor is reminiscent of the CDC-6600 Scoreboard, an early dynamically scheduled processor architecture [22]. A different with the CDC-6600 is that the compiler conveys more explicit information for managing the scoreboard, in the form of the dependence bit vectors. Besides, even though the superscalar processor is an effective way of exploiting ILP, this superscalar processor architecture requires complex devices and the impact of such complexity on the design cost and clock cycle time can be severe [20,21]. Consequently, the superscalar processor will not be evaluated in this paper.

The rest of the paper is organized as follows. Section 2 compares issue slots and instruction pipelines of various ILP processors, Section 3 introduces the DISVLIW

processor architecture and instruction pipeline, in Section 4 we evaluate a performance of the DISVLIW processor, and conclusion follows in Section 5.

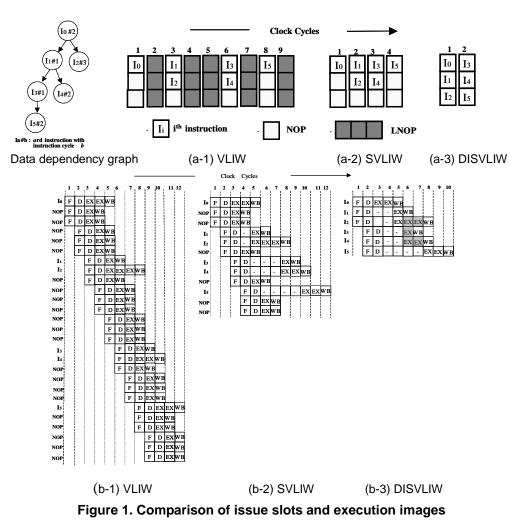

#### 2. Instruction level parallelism

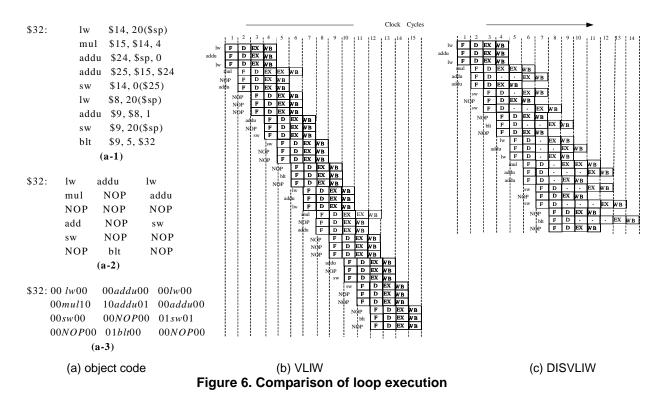

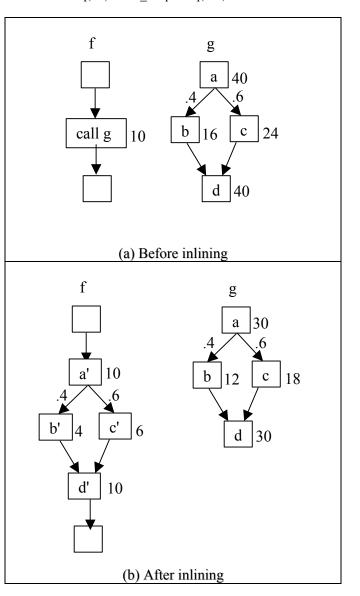

Figure 1 shows issue slots and execution images of the VLIW, the SVLIW, and the DISVLIW processors. The processors execute their own object code generated from given data dependency graph. In the data dependency graph, a node represents an instruction and a directed edge is annotated with data dependencies and resource collisions between instructions. We assume that every processor has three untyped functional units that can execute any instruction and a long instruction has three instructions. Figure 1 illustrates issue slots of each object code using rectangles repeated in the horizontal direction to represent consecutive clock cycles. Squares placed vertically in each rectangle represent the per cycle utilization instruction issue slots, where a rectangle and a square mean a long instruction and an instruction. An instruction is executed in the following four stages: F

(Fetch), D (Decode), EX (EXecute), and WB (Write Back).

Figure 1(b-1) shows an execution image for the VLIW processor to execute VLIW code. The VLIW code contains a number of LNOPs and NOPs in order to solve data dependencies and resource collisions between long instructions as shown in Figure 1(a-1). During execution, the VLIW processor does not allow the next long instruction to enter into the execution stage until functional units have finished executing all instructions within the scheduled long instruction.

Figure 1(b-2) shows an execution image for the SVLIW processor to execute SVLIW code. The SVLIW code is constructed by removing all LNOPs from the VLIW code as shown in Figure 1(b-2).

In order to execute the SVLIW code, the SVLIW processor schedules the next long instruction after checking for data dependencies and resource collisions with the scheduled long instructions in advance. When a collision occurs, the processor is stalled as indicated by dash (–) in Figure 1(b-2) until all collisions are resolved. The SVLIW processor uses the same scheduling strategies used for the VLIW processor.

Figure 1(b-3) shows an execution image for the DISVLIW processor proposed in this research. Since instructions within a long instruction may depend on each other as shown in Figure 1(a-3), we assume that each instruction contains dependency information in order to achieve synchronization. The DISVLIW processor issues one long instruction per cycle and dynamically executes each instruction using dependency information. As shown in the shaded pipelines in Figure 1(b-3), instructions I<sub>2</sub>, I<sub>3</sub>, and I<sub>4</sub> are simultaneously executed during the 6<sup>th</sup> clock cycle although the instructions are fetched on different clock cycle. Instructions I<sub>2</sub> and I<sub>4</sub> are also executed during the 7<sup>th</sup> clock cycle at the same time.

This example demonstrates the process by which the DISVLIW processor can achieve better performance in comparison to the VLIW or the SVLIW processor. The main insight is that in the DISVLIW processor each instruction within a given long instruction is dynamically processed. Therefore, the DISVLIW processor decreases the waiting time to process a given set of long instructions in comparison to other processors.

#### 3. DISVLIW processor architecture

#### 3.1 Long instruction format

To dynamically schedule VLIW instructions, the DISVLIW instruction format is augmented to allow dependent information to be placed in the same VLIW instruction. Dependent information is added to the instruction format to enable synchronization between prior and subsequent instructions.

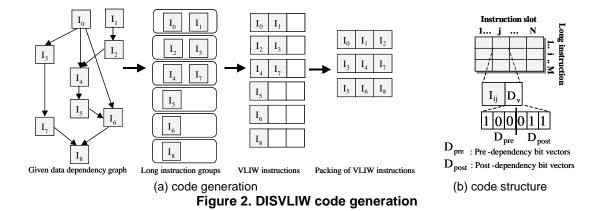

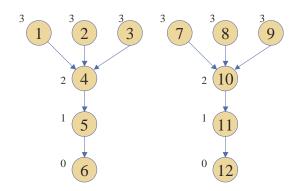

The problem of optimal DISVLIW code generation can be subdivided into two phases as shown in Figure 2. In the remainder of this paper we will refer to the first phase as *VLIW instruction generation* and to the second phase as *packing*; the result of both phases represents the final DISVLIW code composed of long instructions. Each long instruction has multiple instructions that may depend on each other due to data dependencies or resource collisions.

In the VLIW instruction generation phase, the compiler first generates VLIW code from given data dependency graph where each instruction is assigned to a long instruction as shown in Figure 2. The result is a sequence of long instructions so that one long instruction can be executed per clock cycle without violating data dependences or resource constraints. Empty instruction slots within a long instruction have to be filled with *NOPs* (NOPs are depicted with a white background). In the packing phase, the compiler constructs DISVLIW code by removing nearly all LNOPs and NOPs from the generated VLIW code and by inserting dependency information to each instruction.

То store the dependency relations between instructions, each instruction format consists of an instruction I<sub>ii</sub> and dependency vector D<sub>V</sub>, which has predependency D<sub>pre</sub> and post-dependency D<sub>post</sub>. I<sub>ij</sub> refers to the  $j^{th}$  (j=1,..,N) instruction within the  $i^{th}$  (i=1,..,M) long instruction. D<sub>pre</sub> provides information about functional units executing prior instructions that have dependencies with I<sub>ii</sub>. D<sub>post</sub> provides information about functional units that will execute subsequent instructions that depend on  $I_{ij}$ .  $D_{pre}$  and  $D_{post}$  are individually composed of a bit vector that has (N-1) bits, where N equals the number of functional units. To store the information to a bit vector, the compiler allocates one bit for every other functional unit. If  $I_{ij}$  depends on a prior instruction  $I_{lk}$  (k<j if l=i;k=1,..,n if l<i) being executed by functional unit  $F_{k}$ . the bit designating  $F_k$  in the  $D_{pre}$  is set to 1. Otherwise, it is set to zero. Although DISVLIW code contains dependency information composed of many bits, the processor can still achieve a reduction in object code size in comparison to the VLIW processor [21]. Figure 2(b) shows the example of DISVLIW code (N=4).

#### **3.2 DISVLIW processor implementation**

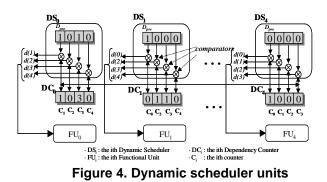

Figure 3 shows the DISVLIW processor architecture. The DISVLIW processor has FU (Functional Unit) and DS (Dynamic Scheduler) pairs, a number of IQs (Instruction Queue) and DCs (Dependency Counter), a register file, an instruction cache, a data cache, and a BTB (Branch Target Buffer). IQs are placed in front of each FU. It seems like instructions within a IQ issue in order, but instructions among IQs slip with respect to each other, dynamic scheduling allows instructions in different IQs(i.e. different FUs) are synchronized by having counters (DC) at each FU. If there are N FUs, then each FU has a DC composed of N-1 counters, 1 counter for every other FU. Each DC saves D<sub>post</sub> of executed instructions on the associated FU. Using the DC, each DS dynamically decides whether to assign the next instruction to the associated FU, or to stall the FU due to resource collisions or data dependencies. The processor also utilizes the BTB structure for branch prediction [6,9].

Every DS checks for data dependencies and resource collisions among instructions per each cycle using both D<sub>pre</sub> of the next instruction and counter values in the associated DC. In Figure 4, we assume that the DISVLIW processor has five pairs of FU and DS. In order to schedule instruction, Each DS compares D<sub>pre</sub> of the next instruction to counter values in the associated DC per each cycle. If any bit in D<sub>pre</sub> is set to 1, DS checks the counter in the corresponding location in the DC. If the counter is 0, it means that the execution of prior dependent instruction hasn't finished. That is, d(i) returns zero. Otherwise, the execution of prior dependent instruction has finished. That is, d(i) returns 1. After the DS confirms that the execution of all prior dependent instructions is finished (all of d(i) return 1), the DS decrements the counter values in corresponding location in its DC using the set bits in given  $D_{pre}$ . It is necessary to clear the D<sub>post</sub> of the prior instructions from the DC before execution. Simultaneously, each DS individually assigns the next instruction to the associated FU.

As an example of Figure 4,  $DS_0$  checks  $D_{pre}$  (1010) of the next instruction and counter values (1030) in its  $DC_0$ . Since counters in corresponding position in  $DC_0$  are greater than 0,  $DS_0$  decrements counters in  $DC_0$  using set bits in  $D_{pre}$ . As soon as  $DC_0$  turns from (1030) to (0020), then  $DS_0$ assigns the next instruction to  $FU_0$

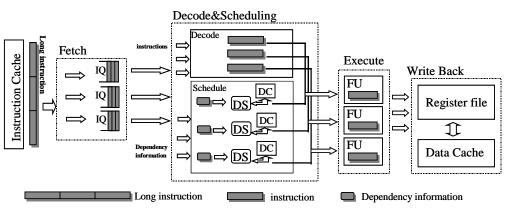

**3.3 Instruction pipeline algorithm**

Each instruction on the DISVLIW processor is executed in four stages as shown in Figure 3. Each stage requires one cycle except the execution stage that requires various execution cycles according to an instruction type. In the Fetch (F) stage, the fetch unit gets one long instruction from the instruction cache each clock cycle and separates it into instructions to store IQs. If IQ is in the full state, the fetch unit cannot fetch the following long instruction, which prevents the IQ from overflowing. In the Decode/Scheduling (D/S) stage, the decode unit analyzes the next instruction at the head of each IQ. Every DS simultaneously checks for data dependencies and resource collisions using both  $D_{pre}$  of the next instruction and counter values in the its DC. If there are no data dependencies and resource collisions,

Figure 3. DISVLIW processor architecture

(a) data dependency graph

(c) Execution steps according to clock cycle

$\cdot$  DC<sub>i</sub> : the ith dependency counter  $\cdot$  C<sub>i</sub> : the ith counter  $\cdot$  FU<sub>i</sub> : the ith functional unit Figure 5. Changes of DC according to instruction execution

each DS decrements counter values in its DC in order to clear the  $D_{post}$  of the prior instructions from its DC and assigns the next instruction to the associated FU. In the Execute (EX) stage, every FU executes instruction and announces to other FUs that its execution will be finished during the execution of the final cycle. To accomplish this, the FU increments counters (indicating the FU) in DCs in corresponding location using set bits in the  $D_{post}$ . Thus, every FU achieves synchronization since it decrements counter values in its DC at D/S stage and increments it at EX stage. To facilitate this, we designed the EX stage with the ability to control the D/S stage. Finally, in the Write Back (WB) stage, the results of the executed instructions are stored in the register file.

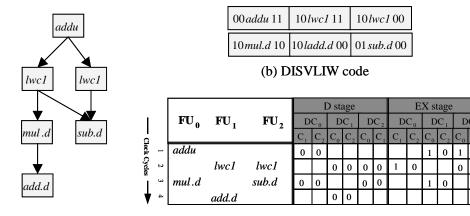

Figure 5 shows execution examples of DISVLIW code generated from Figure 5(a).  $FU_0$  first executes instruction *addu* since the  $D_{pre}$  of *addu* is 00, and simultaneously increments the first counters (indicating FU<sub>0</sub>) in the DC<sub>1</sub> and DC<sub>2</sub> because the  $D_{post}$  of *addu* is 11. Then, FU<sub>1</sub> and FU<sub>2</sub> individually check  $D_{pre}$  bits of the next instruction *lwc1* and the counter values in its DC<sub>1</sub> and DC<sub>2</sub>. If both of them are greater than 0, FU<sub>1</sub> and FU<sub>2</sub> using set bits in the  $D_{pre}$ . It is necessary to clear the  $D_{post}$  of the instruction *addu* from each DC before the execution of FU<sub>1</sub> and FU<sub>2</sub>. Then, FU<sub>1</sub> and FU<sub>2</sub> simultaneously begin the execution of instructions *lwc1*.

#### **3.4 Loop performance**

The DISVLIW processor can significantly reduce the execution cycles of applications containing loops since the processor can simultaneously schedule the instructions fetched from different iterations in the loop.

Figure 6 shows execution images of the VLIW and the DISVLIW processors that execute the  $i^{th}$  iteration

and the  $(i+1)^{th}$  iteration of the loop. We generate VLIW code of Figure 6(a-2) and DISVLIW code of Figure 6(a-3) from the MIPS code of Figure 6(a-1). The MIPS code is to initialize integer array. A long instruction has three instructions each execution cycle of which is one cycle except that those of *mul* are two cycles. Every instruction is executed in the following four pipeline stages: F, D, EX, and WB. Figure 6(b) shows an execution image of the VLIW processor that executes Figure 6(a-2). The VLIW processor requires 15 cycles to execute two iterations of the loop. Figure 6(c) shows an execution image of the DISVLIW processor that executes Figure 6(a-3). Intructions addu and sw are simultaneously executed for the  $6^{th}$  cycle although the instructions are individually fetched at the 2<sup>nd</sup> and the 3<sup>rd</sup> clock cycle. Besides, instructions *blt* and lw are simultaneously executed at the 8<sup>th</sup> cycle although the instructions are fetched from different iterations. The DISVLIW processor requires 14 cycles to execute two iterations of the loop.

0

1

From the above observation, we know that the DISVLIW processor is more effective than the VLIW processor in applications containing loops. This is because the DISVLIW processor can simultaneously schedule instructions fetched from different iterations of the loop as long as the instructions don't depend on each other. Due to this feature, the larger the number of loop iterations the DISVLIW processor gets reduced execution cycles in proportion to those, when compared with the VLIW processor. Although is not shown in the Figure 6, the DISVLIW processor can reduce fetch because the DISVLIW cvcles processor can simultaneously fetch a number of instructions that may depend on each other in a long instruction. The DISVLIW processor also has relative low cache miss rates due to its reduced object code [21].

#### 4. Experiment and analysis

#### 4.1 Simulation system

The performance of the DISVLIW processor was accurately analyzed using a simulator testbed. Using the simulator testbed, we measured the total number of execution cycles for various numerical benchmark applications on the VLIW, the SVLIW, the DISVLIW processor architectures.

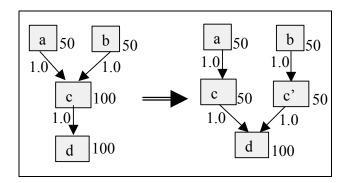

The simulator starts with the MIPS assembler, a Mipspro C++ compiler using optimization flag -O and assembly code generation flag -S, generating MIPS R4000 assembly code by compiling a C-language benchmark applications [17]. Next, the macro expander inputs the MIPS R4000 assembly code while simultaneously expanding macros. The Macro expander then passes the assembly code to each parallelizer. Three parallelizers, each of which is associated with a unique processor, are designed with the ability to exploit ILP across basic blocks using compile techniques such as register renaming, branch prediction, invariant code motion from loops, common subexpression elimination. function inlining, and loop unrolling [6,9,10,11]. Generally, the VLIW's effectiveness depends on how good the compiler is: the VLIW processor using a compiler with higher ILP will produce better performance, and will get higher cache hit rates because of the reduced object code size. However, the DISVLIW processor accomplishes this same goal since it constructs object code

using the VLIW code. In the diagram, VLIW<sub>c</sub>, VLIW<sub>s</sub>, and VLIW<sub>DIS</sub> correspond to VLIW, SVLIW, and DISVLIW code, respectively. The parallelizers then use the MIPS code to generate parallelized code for its processor simulator and then translate this parallelized code into object code.

For these experiments, processor speedups are calculated by dividing the total number of execution cycles of the VLIW processor by the total number of cycles of the DISVLIW or the SVLIW processor. In the Table 1, the fixed parameters and the variable parameters are also shown. Except when stated otherwise, the default values were used in the simulations.

#### Table 1. Input parameters

| Fixed Parameters                   |                                   |  |  |  |  |  |  |  |

|------------------------------------|-----------------------------------|--|--|--|--|--|--|--|

| Processor pipeline                 | Four-stage(F,D,EX, WB)            |  |  |  |  |  |  |  |

| Decoded instruction size           | 4 bytes                           |  |  |  |  |  |  |  |

| integer instruction latency        | 1 cycle                           |  |  |  |  |  |  |  |

| Floating point instruction latency | 1~32 cycle(depend on instruction) |  |  |  |  |  |  |  |

| Data cache size                    | Perfect(no miss penalty)          |  |  |  |  |  |  |  |

| cache mapping method               | direct mapped                     |  |  |  |  |  |  |  |

| cache replacement policy           | LRU(Least Recently Used)          |  |  |  |  |  |  |  |

| Variable                           | Parameters                        |  |  |  |  |  |  |  |

| Parameter                          | Default Value                     |  |  |  |  |  |  |  |

| A number of integer unit           | 2                                 |  |  |  |  |  |  |  |

| A number of floating-point unit    | 2                                 |  |  |  |  |  |  |  |

| next long instruction miss penalty | 4                                 |  |  |  |  |  |  |  |

| Instruction cache size             | 16k bytes                         |  |  |  |  |  |  |  |

Table 2 provides the benchmark applications and the proportion of I/F (Integer instructions and Floating-point instructions) of each benchmark application. These applications all use double precision.

| Benchmarks | Description                                       | I/F(%)    |

|------------|---------------------------------------------------|-----------|

| LIVERMORE  | Do loop for various kernel operations             | 65.3/34.7 |

| ММ         | Matrix Multiply using floating point instructions | 68.4/31.6 |

| CLINPACK   | Set of linear algebra subroutine                  | 75.7/24.3 |

| WHETSTONE  | Loop instructions for arithmetic computation      | 65.6/34.4 |

| FFT        | Matrix Fourier Transformation                     | 43.3/56.7 |

Table 2. Benchmark applications

Table 3 tabulates the ratios of object code size of the VLIW to both the SVLIW and DISVLIW processors for each benchmark. In this experiment, we chose numerical benchmarks that have a high proportion of floating-point instructions. This choice was appropriate because the DISVLIW processor is more effective given dynamic instruction scheduling and reduced object code size. Even though VLIW<sub>DIS</sub> contains many bits of dependency information, Table 3 indicates that VLIW<sub>DIS</sub> averages 45% smaller than VLIW<sub>c</sub> and is almost the same size as VLIW<sub>s</sub>.

| Tab | ole 3. | Comparis | on of ol | oject cod | de size |

|-----|--------|----------|----------|-----------|---------|

|-----|--------|----------|----------|-----------|---------|

| Benchmarks | VLIW <sub>c</sub> | VLIW s | VLIW <sub>DIS</sub> |

|------------|-------------------|--------|---------------------|

| LIVERMORE  | 1                 | 0.723  | 0.725               |

| M M        | 1                 | 0.568  | 0.591               |

| CLINPACK   | 1                 | 0.673  | 0.673               |

| WHETSTONE  | 1                 | 0.438  | 0.385               |

| FFT        | 1                 | 0.385  | 0.400               |

| AVERAGE    | 1                 | 0.557  | 0.554               |

#### **4.2 Experimental results**

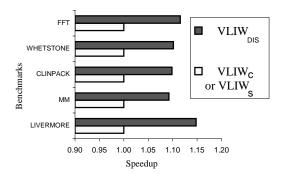

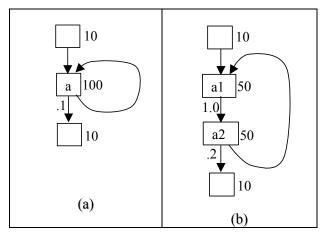

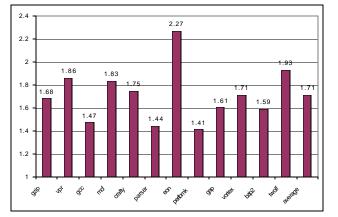

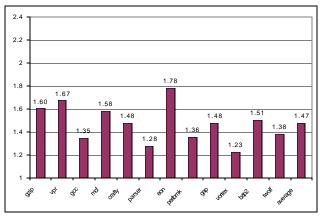

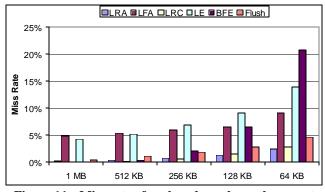

Figure 7 shows the speedup of the DISVLIW processor over the VLIW (or the SVLIW) processor using different scheduling strategies. In order to evaluate scheduling performance only, we ignore cache effects such as cache miss rates. We assume that an instruction cache size is perfect (no miss penalty). In this experiment, we reduced the number of loop iterations in each benchmark application to reduce simulation duration.

Figure 7 illustrates that even though we assume a cache with a zero miss rate, the DISVLIW's performance is still 9%-15% higher than that of the VLIW processor regardless of benchmark application. We have the DISVLIW's scheduling strategies to thank for this speedup. This scheduling decreases the waiting time to

process a set of long instructions when compared to the VLIW and SVLIW processors. By contrast, the VLIW and the SVLIW processor can't execute pending long instructions until the execution of all instructions in the previous long instruction finishes. In Figure 7, the SVLIW processor shows same performance when compared to the VLIW processor.

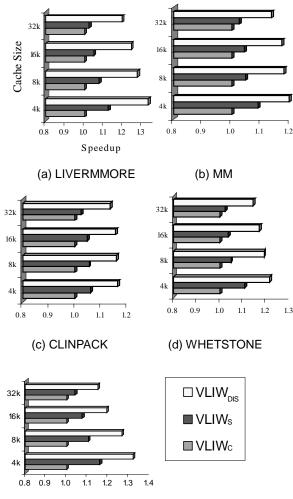

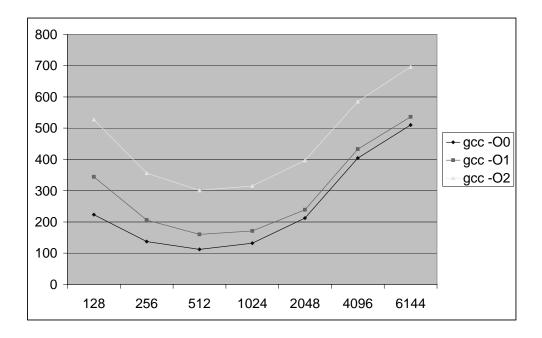

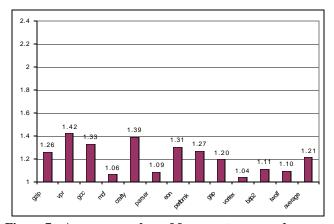

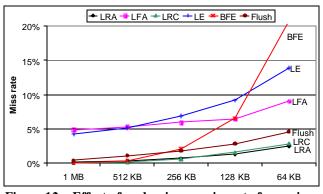

Figure 8 illustrates the impact of cache size on speedups of the DISVLIW processor with respect to both the SVLIW and VLIW processors. We varied the instruction cache size from 4k bytes to 32k bytes to compare performance according to changes in cache size. The speedups of the DISVLIW and the SVLIW processors were measured relative to the VLIW processor regardless of cache size. In this experiment, we also reduced the number of loop iterations in each benchmark to reduce simulation duration.

Figure 7. Comparison of speedups for different scheduling strategies

These results indicates that the DISVLIW processor is faster than the SVLIW processor regardless of both benchmark applications and cache size. This is due to the DISVLIW's unique instruction scheduling strategies. Another factor is the DISVLIW's reduced object code size, which decreases average fetch cycles and also reduces cache misses, as shown in Table 3. Figure 8 indicates that larger cache sizes result in smaller speedup differences between the VLIW and DISVLIW processors. At smaller cache sizes, the VLIW's performance is slower due to higher cache miss rates. Unlike the VLIW, the DISVLIW's performance is not as sensitive to cache size due to its smaller object code. But as cache size increases, performance difference decreases and the VLIW's performance approaches that of the DISVLIW. Yet, even assuming perfect cache, the DISVLIW is still faster than the VLIW's.

Overall, the performance of DISVLIW processor is faster than the VLIW and the SVLIW processors over a wide range of cache size and across various numerical benchmark applications. We attribute these performance gains to the balanced benefits of compile-time and runtime parallelization, dynamic instruction scheduling, and size reduction of object code as previously described.

(e) FFT

### Figure 8. Comparison of the speedups according to changes in cache sizes

#### **5.** Conclusion

This paper describes a new ILP processor architecture referred to as Dynamically Instruction Scheduled VLIW (DISVLIW). The DISVLIW processor is a hybrid architecture that has inherited features as ILP exploitation at compile-time of the VLIW processor and dynamic scheduling at run-time of the superscalar processor. The experimental evaluations presented in this paper have shown that the DISVLIW processor achieves a high speedup over the VLIW and the SVLIW processors for a wide range of cache sizes and across various numerical benchmark applications. These performance gains of the DISVLIW processor result from dynamic instruction scheduling and size reduction of object code. The DISVLIW processor architecture opens several new avenues of research. Optimization of dependency information within object code, DISVLIW compilers, and scalability of functional units in the system are just a few examples that will be investigated in future work. Particularly, our research will focus on optimization and management of the dependency information required in order to achieve synchronization.

#### 6. References

[1] Ken Sakamura, '21st-century microprocessors,' IEEE Micro, pp.10~11, July/Aug 2000.

[2] Michael J. Flynn, Computer Architecture, Jones and Bartlett Publishers, 1995

[3] P. P. Chang, D. M. Lavery, S. A. Mahlhe, W. Y. Chen, and Wen-Mei. W. Hwu, "The Importance of Prepass Code Scheduling for Superscalar and Superpipelined Processors," IEEE Transactions on Computers, Vol. 44, No. 3, pp. 353~370, March 1995.

[4] Shyh-Kwei Chen, W. Kent Fuchs, and Wen-Mei W. Hwu, "An analytical approach to scheduling code for superscalar and VLIW architectures," Proc. International Conference on Parallel Processing., pp. I258-I292, 1994.

[5] J. A. Fisher, The VLIW machine: A multiprocessor for compiling scientific code, IEEE Transactions on Computers, pp. 45~53, July 1984.

[6] Barry Fagin, "Partial Resolution in Branch Target Buffers'" IEEE Computers, Vol. 46, No. 10, October 1997

[7] Joseph A. Fisher, "Trace Scheduling: A Technique for Global Microcode Compaction," IEEE Transactions on Computers., Vol. C-30, No. 7, pp. 478~490, July 1981.

[8] Roger Espasa and Mateo Valero, "Exploiting instructionand data-level parallelism," IEEE Micro, Vol. 17, No. 5, Sept 1997.

[9] S. A. Mahlke, R. E. Hank, J. E. M. McCormick, D. I. August, and W. W. Hwu, "A Comparison of Full and Partial Predicated Execution Support for ILP Processors," Proceedings of the 22th international Symposium on Computer Architectures, pp. 138~150, 1995.

[10] Thomas M. Conte and Sumedh W. Sathaye, "Dynamic Rescheduling: A technique for object code compatibility in VLIW architecture," Proceedings of 28th International Symposium on Microarchitecture, March 1995.

[11] Arthur Abnous and Nader Bagherzadeh, "Pipelining and bypassing in a VLIW processor," Transactions on Parallel and Distributed Systems, Vol. 5, No. 6, pp. 658~664, June 1994.

[12] T. M. Conte and S. W. Sathaye, "Dynamic rescheduling; a technique for object code compatibility in VLIW architecture," proceedings of the 28<sup>th</sup> Annual International Symposium on Micro architecture, pp. 208~218, March 1995.

[13] Kevin W. Rudd and Michael J. Flynn, "Instruction-level parallel processors-dynamic and static scheduling tradeoffs," Proc. The Second AIZU International Symposium on Parallel Algorithms/ Architecture Synthesis., pp. 74~80, March 1997.

[14] Shusuke Okamoto and Masahiro Sowa, "Hybrid processor based on VLIW and PN-Superscalar," Proc. DPTA'96 International Conference., pp. 623~632, 1996.

[15] Sunghyun Jee and Sukil Kim, "Performance analysis of caching instructions on SVLIW processor and VLIW processor," Journal IEEE Korea Council, Vol. 1, No. 1, December 1997.

[16] Susan J. Eggers, Joel S. Emer, Henry M. Levy, and Jack L. Lo, "Simultaneous multithreading," IEEE Micro, Vol. 17, No. 5, Sep 1997.

[17] MIPS R4000 Microprocessor User's Manual, MIPS Computer Systems, Inc., 1991.

[19] T. Hara and H. Ando, "Performance comparison of ILP machines with cycle time evaluation," Proceedings of the 23<sup>rd</sup> Annual International Symposium on Computer Architecture, pp. 213~224, Mach 1996.

[20] A. F. de Souza and P. Rounce, "Dynamically Scheduling VLIW instructions," Journal of Parallel and Distributed Computing, pp. 1480~1511, 2000.

[21] Sunghyun Jee and Sukil Kim," A Design of A Processor Architecture for Codes With Explicit data Dependencies," Proc. tenth SIAM Conference on Parallel Processing for Scientific Computing 2001, March 2001.

[22] Patterson D. A., and J. L Hennessy, *Computer Architecture A Quantitive Approach*  $2^{nd}$  *edition*, Morgan Kaufmann, pp. 240~261, 1996.

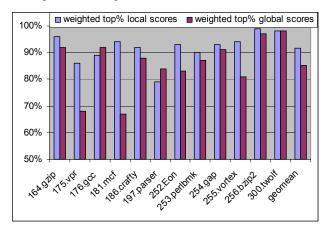

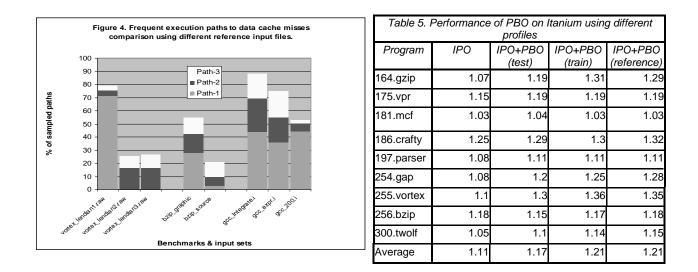

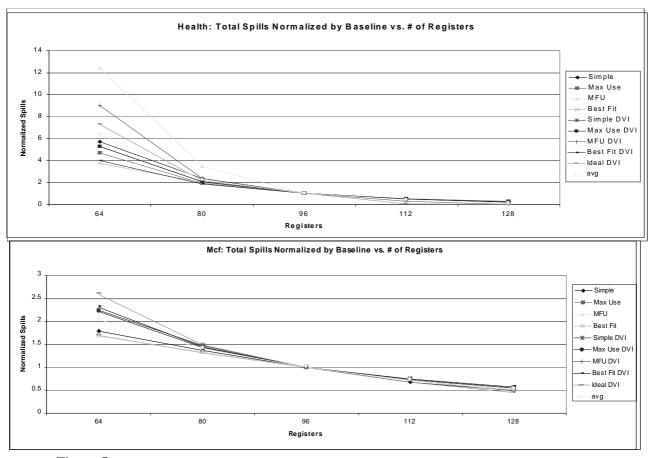

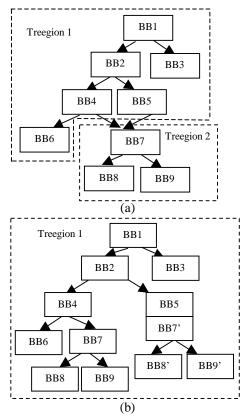

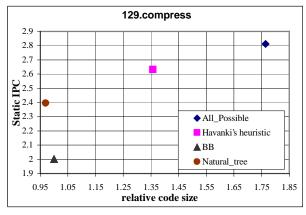

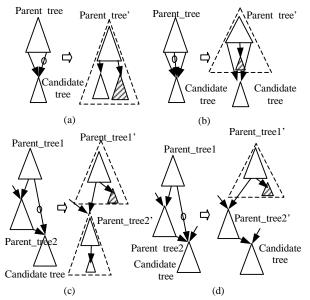

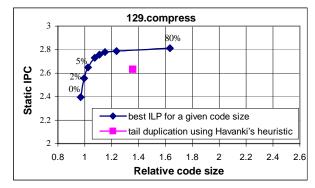

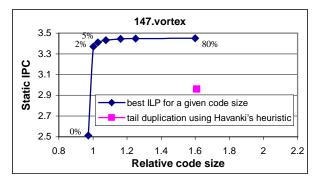

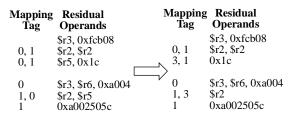

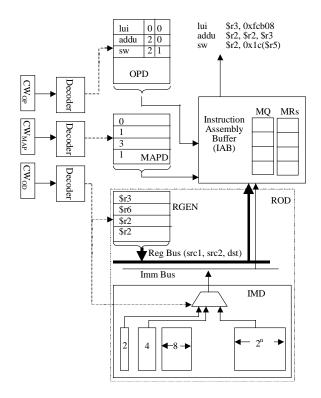

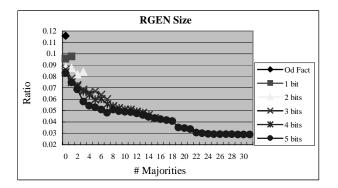

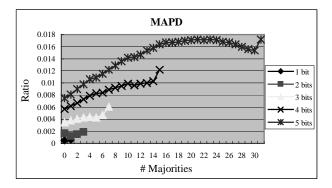

[23] Intel, <u>http://www.intel.com/ia64</u>, *IA-64 Architecture Software Developer's Manual, Volume 1:IA-64 Application Architecture, Revision 1.1*, July 2000.